随着百万门单片FPGA器件的上市, FPGA的故障检测, 尤其是延时故障的检测成为人们关注的热点.然而, 针对FPGA延时故障的检测只有有限的方法.文献[1-3]给出了FPGA故障的内建自测试(BIST)检测方法, 文献[4-6]通过修改查找表(LUT)功能以提高FPGA延时故障的可测性, 文献[7]给出了提升测试故障覆盖率的方法,文献[8]给出了提升边界扫描技术(JTAG)进行延时测试速率的方法,文献[9]将JTAG技术用于单芯片系统级的故障诊断中, 文献[10-11]分别对JTAG指令进行了芯片级和板级的扩充.鉴于边界扫描技术的诸多优点, 本文将研究基于边界扫描测试技术的FPGA延时故障检测技术.目前, 大多数基于SRAM技术的FPGA器件具有符合IEEE 1149.1标准的JTAG电路和指令.例如, XC4006E共有8条JTAG指令, 除可以实现标准中所规定的外测试指令(EXTEST)、采样/加载指令(SAMPLE/PRELOAD)、旁路指令(BYPASS)外, 还包括READBACK(回读)、CONFIGURE(配置)等指令[12-13].本文基于XC4006E系列FPGA, 对其JTAG指令进行扩充, 并对边界扫描电路做相应修改, 使其同时具备板级和芯片级延时故障的检测能力.

1 板级互连延时故障检测 1.1 测试原理IEEE1149.1标准中规定外测试指令(EXTEST指令)可用于板级互连测试[14-15].利用外测试指令进行板级互连测试时, 首先将EXTEST指令加载到指令寄存器中进行指令译码, 并选择相应的边界扫描单元.然后通过TDI串行移入测试向量, 由边界扫描单元中的加载锁存器并行加载/读取测试向量.最后捕捉测试响应, 并由TDO串行移出进行观测.

图 1为利用外测试指令进行板级互连测试时TAP控制器的状态转移图.在TAP控制器进入Update-DR状态后, 测试向量加载时钟updateDR在测试时钟TCK的下降沿输出(左侧实线标出), 在updateDR上升沿测试向量加载; 测试响应捕捉时钟clkDR在测试时钟TCK下降沿输出(右侧实线标出), 数据捕捉在clkDR的上升沿有效.由图 1可知, 测试向量加载(图中updateDR)和测试响应捕捉(图中clkDR)之间相差了2.5个测试时钟TCK.

|

| 图 1 TAP控制器状态转移图 Fig.1 State transition diagram of the TAP controller |

为使外测试指令可用于板级互连延时故障的检测, 必须使测试向量加载和测试响应捕捉在同一个TCK内完成[10].测试时, 可以设置TCK的周期为可接受的最大互连延时.如果选定的互连通路延时小于TCK的周期, 那么测试向量从TDI加载至芯片1的输出管脚后, 在芯片2的管脚即可捕捉到测试响应, 则芯片2的TDO可以串行移出测试响应数据; 如果选定的互连延时大于TCK的周期, 则测试向量加载至芯片1后, 芯片2无法捕捉到测试响应数据, 即可认为通路上存在延时故障.调节TCK的周期, 就可进行板级互连延时故障的检测.

显然, 当updateDR和clkDR位于一个TCK周期内时, 测试向量加载和测试响应捕捉将在一个时钟周期内完成.这可以通过将updateDR延迟1.5个TCK或将clkDR提前1.5个TCK实现.在IEEE1149.1标准中规定, clkDR的产生依赖于Capture-DR和Shift-DR两个状态, 而updateDR仅和Update-DR状态有关.因此, 选择延迟updateDR.

1.2 硬件电路设计及仿真针对EXTEST指令扩展, 对硬件电路进行如下修改.

(1) 增加的updateDR时钟延迟模块, 如图 2所示,由两级D触发器和一个与门实现.其中第一级D触发器的输入为原始的updateDR信号, 来自于TAP控制器的输出, 第二级D触发器的输入为第一级D触发器的输出, 两级D触发器的时钟信号均为测试时钟TCK.与门的2个输入分别为经过两级D触发器延时的updateDR和TCK, 输出se_updateDR即为延迟后的数据加载时钟.由图 1的波形图可知, clkDR在TCK的正边沿输出, 而updateDR则在TCK的负边沿输出, 当updateDR经过两级负边沿有效的触发器延迟后与TCK相与, 其输出sel_updateDR正好和clkDR在一个TCK周期内, 即实现将updateDR时钟延迟1.5个TCK.

|

| 图 2 updateDR时钟延迟电路 Fig.2 Clock delay circuit of updateDR |

(2) 修改指令译码器.板级互连测试和修改后的updateDR只在外测试指令加载后有效, 因此, 在指令译码器中加一个选通控制信号sel_update, 用于选择输出原始的updateDR还是延迟的updateDR.此选通控制信号只在外测试指令加载后输出, 以确保除外测试指令外的其它指令的updateDR均为原始的updateDR时钟.

(3) 修改TAP控制器.为了使得在外测试指令下输出sel_updateDR, 在其他指令下输出updateDR, 在TAP控制器外围增加了时钟延时模块和一个二选一多路选择器.

修改后各模块相应的连接关系和仿真波形如图 3所示.图 3(a)为TAP控制器, 输出的控制信号连接到指令寄存器(图中JTAG_ir)和指令译码逻辑(图中JTAG_ir_dec2) 中.时钟延迟模块(图中JTAG_delay)的两个输入为TCK和原始的加载时钟updateDR, 用于产生延迟加载时钟sel_updateDR.右侧多路选择器的输入为原始加载时钟和延迟加载时钟, 其选通端为指令译码器输出的sel_update控制信号.当sel_update信号为1时, 输出延迟的加载时钟.反之, 当sel_update为0时, 输出原始加载时钟.由图 3(b)可见, 修改后的TAP控制器在外测试指令(二进制码为000, 图中bus{IR2, IR1, IR0}=0) 加载后输出sel_updateDR, 其有效沿(上升沿, 图中左侧实线标示)和clkDR有效沿(上升沿, 图中右侧实线标示)在一个TCK内, 而当加载/采样指令(二进制码为001) 和旁路指令(二进制码为111) 加载后输出updateDR时钟信号.

|

| 图 3 修改后的TAP控制器原理图及波形 Fig.3 The schematic and waveform of the modified TAP controller |

由板级延时故障检测指令(扩展后的EXTEST指令)可以看出, 所能检测到的延时故障必须大于测试时钟TCK的周期, 若待测路径的延时小于TCK的周期, 则无法检测到.然而在芯片设计中, 可接受的延时非常小.因此, 引入外部可编程的测试时钟, 用于芯片中基于路径的延时故障检测.

2.1 测试原理选用外部振荡源为被测电路提供测试时钟.测试时, 首先通过芯片TDI管脚移入测试向量, 用以待测路径的选择和敏化, 测试时钟通过芯片输入边界扫描单元加载至待测路径.同时, 测试时钟也连至传输检测电路, 作为检测电路的采样时钟[11].调节测试时钟的半周期为待测路径允许的最大延时时间Tmax.如果待测路径延时小于Tmax, 检测器将检测到通过路径传输的响应时钟, 如果待测路径延时大于Tmax, 检测器将无法检测到沿路径传输的响应时钟信号.如果测试时钟为可编程的时钟, 即周期可调, 将能更准确的检测到路径延时.

2.2 硬件电路设计及仿真芯片延时故障测试原理涉及测试时钟、指令译码逻辑、边界扫描单元和检测电路等模块, 对各电路模块进行如下修改.

(1) 增加的测试时钟可以选用系统芯片时钟, 也可选用可编程的外部时钟.对于外部测试时钟, 从测试电路的稳定角度考虑, 应滤除外部测试时钟的第一个周期[11].因此, 测试时钟模块由外部振荡源和脉冲滤除电路组成.

(2) 修改指令译码逻辑.XC4006E芯片JTAG指令有2个用户测试指令USER1和USER2, 其二进制码分别为010和011, 文中选用USER1作为芯片路径延时故障检测指令.该指令加载后, 指令译码逻辑输出2个新增的控制信号:外部测试时钟模块的使能信号EN及边界扫描单元中四选一多路选择器的选通信号mode和sel_osc.其中EN用于启动外部振荡源, 当EN为0→1时, 外部振荡源输出外部测试时钟.多路选择器的选通信号用于选定输入边界扫描单元测试时钟和输出边界扫描单元响应时钟状态, 当{mode, sel_osc}=2′b11时该状态有效.

(3) 对于边界扫描单元, 为了能加载外部测试时钟并输出响应时钟, 将输入、输出边界扫描单元加载锁存器后连接的二选一多路选择器换成四选一多路选择器, 修改后的边界扫描单元如图 4所示.

|

| 图 4 边界扫描单元修改示意图 Fig.4 The revised schematic of the boundary scan |

图 4中四选一多路选择器的2个选通信号mode和sel_osc均来自于指令译码逻辑.当{mode, sel_osc}=2′b00时, 输入、输出边界扫描单元均输出芯片系统数据, 执行正常的芯片管脚功能; 当{mode, sel_osc}=2′b10时, 输入、输出边界扫描单元均输出加载锁存器中的数据, 执行正常的边界扫描单元功能; 当{mode, sel_osc}=2′b11时, 输入边界扫描单元输出外部测试时钟信号, 实现测试时钟的加载, 输出边界扫描单元输出系统输出管脚数据, 即为沿待测路径传输后的响应时钟.这样, 修改后的边界扫描单元可以执行正常的管脚功能, 正常的边界扫描单元功能和USER1指令下测试时钟加载、测试响应输出3种功能, 与IEEE1149.1标准完全兼容.

(4) 检测电路由双边沿D触发器和一个二输入异或门组成[11], 图 5为检测电路的仿真波形.可以通过观察在测试时钟的第一个半周期检测电路的输出是否发生1→0→1的跳变来检测待测路径是否存在延时故障[11].图 5中的波形图显示了正常通路(图中td_out信号)和故障通路(图中td_out1信号)的输出波形区别, 图中实线标出检测电路的采样沿, 可以看到正常通路在测试时钟(图中osc_delay信号)的第一个半周期内发生了1→0→1跳变,而故障通路则没有.

|

| 图 5 检测电路波形 Fig.5 The waveform of the detection circuit |

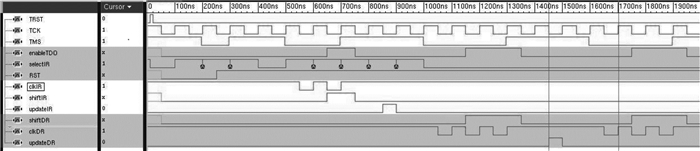

对修改后的XC4006E边界扫描电路进行仿真, 得到扩充后的JTAG指令波形, 如图 6所示.

|

| 图 6 扩充后的JTAG指令波形 Fig.6 The waveform of the extended JTAG instruction |

图 6(a)加载的指令依次为BYPASS指令(图中bus{IR2, IR1, IR0}=7)、SAMPLE/PRELOAD指令(图中bus{IR2, IR1, IR0}=1) 及扩展后的EXTEST指令(图中bus{IR2, IR1, IR0}=0).可以看出, 当前加载指令为扩展后的EXTEST时, 测试向量加载时钟(图中sel_updateDR_de信号)和测试响应捕捉时钟(图中clkBSC信号)在一个TCK周期内.图 6(b)加载的指令依次为USER1指令(图中bus{IR2, IR1, IR0}=2)、CONFIGURE指令(图中bus{IR2, IR1, IR0}=5) 及READBACK指令(图中bus{IR2, IR1, IR0}=4).可以看出, 当前加载指令为USER1时, 外部测试时钟使能信号(图中EN信号)为高电平, 外部测试时钟(图中osc_delay信号)有效.当前指令为XC4006E原有的JTAG指令时, TAP控制器和指令译码逻辑均可正确输出相应的控制信号.

4 结束语通过扩展XC4006E芯片的JTAG指令, 提出一种基于边界扫描技术的FPGA延时故障检测方法.通过扩充EXTEST指令和USER1指令,修改边界扫描电路来完成板级互连延时故障和芯片级路径延时故障的测试.仿真结果表明, 扩展后的XC4006E的JTAG指令不仅与原指令功能兼容, 还可以实现板级和芯片级延时故障的检测.

| [1] | MISHRA Bharti, JAIN Rita, SARASWAT Richa.Low power BIST based multiplier design and simulation using FPGA[C]//2016 IEEE Students' Conference on Electrical, Electronics and Computer Science (SCEECS).Washington D C:IEEE, 2016:1-6. |

| [2] | HUSSAIN Siam U, MAJZOOBI Mehrdad, KOUSHANFAR Farinaz. A built-in-self-test scheme for online evaluation of physical unclonable functions and true random number generators[J]. IEEE Transactions on Multi-Scale Computing Systems, 2016, 2(1): 2-16 DOI:10.1109/TMSCS.2016.2519902 |

| [3] | EBRAHIM Ali, ARSLAN Tughrul, ITURBE Xabier.A fast and scalable FPGA damage diagnostic service for R3TOS using BIST cloning technique[C]//201424th International Conference on Field Programmable Logic and Applications (FPL).Washington D C:IEEE, 2014:1-4. |

| [4] | ALAM Md Mahbub, TEHRANIPOOR Mark, FORTE Domenic.Recycled FPGA detection using exhaustive LUT path delay characterization[C]//2016 IEEE International Test Conference (ITC).Washington D C:IEEE, 2016:1-10. |

| [5] | ALMURIB Haider A F, NANDHA KUMAR T, LOMBARDI Fabrizio. Scalable application-dependent diagnosisof interconnects of SRAM-based FPGAs[J]. IEEE Transactions on Computers, 2014, 63(6): 1540-1550 DOI:10.1109/TC.2013.34 |

| [6] | HAQUE Mubin Ul, SWORNA Zarrin Tasnim, HASAN BABU Hafiz Md.An improved design of a reversible fault tolerant LUT-based FPGA[C]//201629th International Conference on VLSI Design and 201615th International Conference on Embedded Systems (VLSID).Washington D C:IEEE, 2016:445-450. |

| [7] | BAUER Lars, BRAUN Claus, IMHOF Michael E, et al. Test strategies for reliable runtime reconfigurable architectures[J]. IEEE Transactions on Computers, 2013, 62(8): 1494-1507 DOI:10.1109/TC.2013.53 |

| [8] | GRUWELL Ammon, ZABRISKIE Peter, WIRTHLIN Michael.High-speed FPGA configuration and testing through JTAG[C]//2016 IEEE AUTOTESTCON.Washington D C:IEEE, 2016:1-8. |

| [9] | UNGAR Louis Y. Boundary scan as a system-level diagnostic tool[J]. IEEE Instrumentation & Measurement Magazine, 2013, 16(4): 8-15 |

| [10] | PARK Sungju, KIM Taehyung.A new IEEE 1149.1 boundary scan design for the detection of delay defects[C]//Proceedings of Design, Automation and Test in Europe Conference and Exhibition 2000.Washington D C:IEEE, 2000:458-462. |

| [11] | TAN Tek Jau, LEE Chung Len.Socillator test:A delay test scheme for embedded ICs in the boundary-scan environment[C]//19th IEEE Proceedings on VLSI Test Symposium.Washington D C:IEEE, 2001:158-162. |

| [12] | XILINX.XC4000E and XC4000X series field programmable gate arrays[EB/OL]. (1999-05-04).http://www.xilinx.com/support/documentation/data_sheets/4000.pdf. |

| [13] | LAKSHMINARAYANAN G, VENKATARAMANI B, SENTHILKUMAR K P, et al.Design and implementation of FPGA based wavepipelined fast convolver[C]//2000 TENCON Proceeding Kuala Lumpur, Malaysia:IEEE, 2000:212-217. |

| [14] | ROSENFELD Kurt, KARRI Ramesh. Attacks and defenses for JTAG[J]. IEEE Design & Test of Computers, 2010, 27(1): 36-47 |

| [15] | ARYA Namita, SINGH Amit Prakash.IEEE 1149.1 test acess part (JTAG) verification using verilog simulation[C]//International Conference on Electrical, Electronics, and Optimization Techriques.India:Chennai, 2016:106-111. |